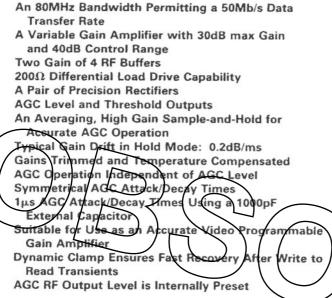

FEATURES

#### PRODUCT DESCRIPTION

The AD890 is primarily intended for high-performance disk subsystem use and as such it is configured around the classic read channel processing block diagram. It is intended to be connected between the head preamplifier and the qualification circuitry required for digital data recovery. When used with the AD891 rigid disk data qualifier, data transfer rates in excess of 50Mb/s can be processed.

A temperature-compensated AGC loop, with an exponential transfer characteristic, permits optimal settling and allows for predictable performance in the classic single integrator control loop configuration. Fast acquisition and low droop while in the hold mode allow for AGC operation to be performed within the sector header without compromising channel behavior when reading data.

The AD890 processing element has the flexibility to perform both continuous and sampled AGC functions; it is also ideal for embedded, dedicated, or mixed servo applications. Two userdefined filter/equalizer stages may be employed, thus allowing maximum design flexibility. This greatly simplifies the design of the overall channel characteristics. Using the AD890, the designer no longer needs to resort to passive techniques to isolate network functions; this avoids problems of signal loss and interaction. Two low-offset, 100MHz full-wave rectifiers provide the capability to track a 1V peak signal. The rectifier generating the "Qualifier

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

## Precision, Wideband Channel Processing Element

Threshold" output may be used for creating a data qualification level. A second redtifier is used to drive the sample-and-hold circulary.

he

behavior

up

80MHz bandwidth of the AD890 ensures good phase linearity

o 50MHz. Thus, data transfer rates in excess of 50Mb/s can

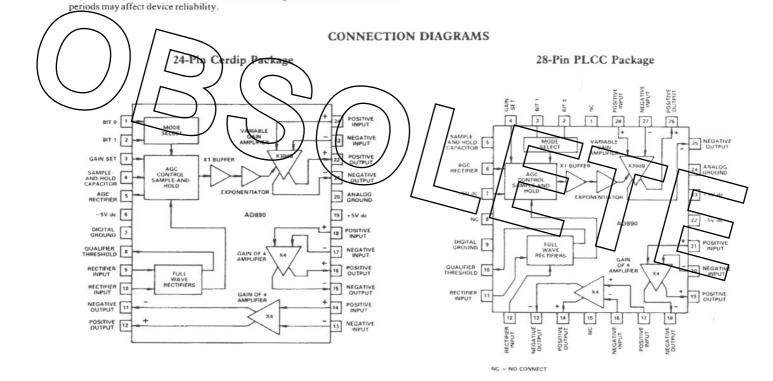

The AD890 is available in both a 24 pin, slim-line cardip package and in a 28-pin PLCC package and is specified to operate over the 0 to 70°C commercial temperature range.

be supported with good error rates and predictable channel

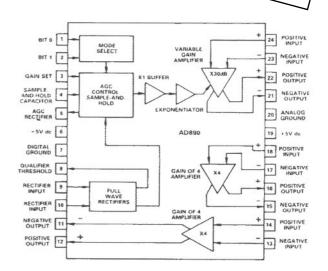

#### Functional Block Diagram

| One Technology Way | ; P. O. Box 9106; | Norwood, MA 02062-9106 |

|--------------------|-------------------|------------------------|

| Tel: 617/329-4700  |                   | TWX: 710/394-6577      |

| West Coast         | Central           | Atlantic               |

| 714/641-9391       | 214/231-5094      | 215/643-7790           |

# **SPECIFICATIONS** (@+25°C and ±5V dc, unless otherwise noted)

| Model                                                                                                                                                                               | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Min                      | AD890J<br>Typ                | Max                            | Units                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------------|--------------------------------|-------------------------------------------|

| VARIABLE GAIN AMPLIFIER<br>Maximum Gain <sup>1</sup><br>± 3dB Bandwidth<br>Input Voltage Noise<br>Input Signal Range<br>Input Resistance<br>Output Impedance<br>Harmonic Distortion | Up to 26dB Gain Reduction<br>0dB Gain Reduction, f = 1kHz<br>Recommended p-p Differential<br>0dB Gain Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>29.4</b><br>100<br>10 | 30.0<br>5<br>12<br>5<br>0.15 | <b>30.6</b><br>200             | dB<br>MHz<br>nV/√Hz<br>mV<br>kΩ<br>Ω<br>% |

| Output dc Level                                                                                                                                                                     | 26dB Gain Reduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | 1.5<br>3.5                   |                                | %<br>V                                    |

| INPUT CLAMP <sup>2</sup><br>Turn-On Time<br>Turn-Off Time<br>Input Signal Attenuation<br>On-State Input Impedance                                                                   | Differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 30<br>200<br>35<br>14        |                                | ns<br>ns<br>dB<br>Ω                       |

| GAIN OF 4 BNFFER<br>Nominal Vain<br>Gain Variation<br>± 3dB Bandwidth<br>nput Voltage Noise <sup>3</sup><br>Input Resistance                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12.50<br>160<br>100      | 12.75<br>±0.25<br>7          | 13.00                          | dB<br>dB<br>MHz<br>nV/√Hz<br>kΩ           |

| Input Common Molic Range<br>Output Resistance<br>Harmonic Distortion<br>Output Signal Level<br>Output dc Level                                                                      | 300my Peak Output, 200Ω Load<br>Recommended p.p Differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7 - 1.5                  | 10<br>0.20<br>V.9<br>2.5     | + 1.5                          |                                           |

| FULL WAVE RECTIFIER<br>Input Signal Level<br>– 3dB Bandwidth<br>dc Offset <sup>4</sup>                                                                                              | p-p Differential<br>100mV (a 1V Peak Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          |                              | 3<br>±20                       | MH                                        |

| AGC CONTROL SECTION<br>Attack Time                                                                                                                                                  | 26dB Gain Step – 1000pF C <sub>SAMPLE</sub><br>26dB Gain Step – < 50pF C <sub>SAMPLE</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                          | 1.0<br>120                   |                                | μ5                                        |

| Hold Time<br>AGC Control Range<br>AGC Control Sensitivity<br>AGC Control Linearity<br>Set Level Input Range                                                                         | 1dB Gain Change – 1000pF C <sub>SAMPLE</sub><br>Per 20mV Input<br>26dB AGC Range<br>For Specified Accuracy<br>Nondestructive Input Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 36<br>0<br>- 0.3         | 10<br>40<br>1                | ±0.5<br>800<br>V <sub>CC</sub> | ms<br>dB<br>dB<br>dB<br>mV<br>V           |

| MODE CONTROL SECTION<br>TTL Compatible<br>V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub><br>I <sub>IH</sub><br>I <sub>IL</sub><br>Mode Switching Times                       | Amerikan in Second Seco | 2.0                      |                              | 0.8<br>100<br>2.0<br>50        | V<br>V<br>nA<br>µA<br>ns                  |

| POWER SUPPLY REQUIREMENTS<br>Rated Performance<br>Operating Range<br>Quiescent Current<br>V <sub>CC</sub><br>V <sub>EE</sub>                                                        | T <sub>min</sub> to T <sub>max</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ±4.6<br>44<br>18         | ± 5,0<br>60<br>28            | ± 6.5<br>76<br>40              | V<br>V<br>mA<br>mA                        |

NOTES Gain calibrated in gain set mode with 0 volts applied to the Gain Set Pin.

<sup>2</sup>Clamp operation is specified with a source impedance of 200Ω in series with  $0.1 \mu F$ .

<sup>3</sup>Over the full 100MHz bandwidth of the AD890, the worst-case rms signal-to-noise ratio is 40dB or better with a 40dB AGC range.

<sup>4</sup>Measured using a 4k\Omega resistor connected between the Qualifier Threshold Pin and V\_{EE}

Specifications subject to change without notice.

All min and max specifications are guaranteed. Specifications in boldface are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels.

<sup>1</sup>28-pin PLCC package:  $\theta_{1A} = 100^{\circ}C/W;$

24-pin cerdip package: 0JA = 55°C/W.

NOTE

| ABSOLUTE MAXIMUM RATINGS*                                                | Logic Ass              |

|--------------------------------------------------------------------------|------------------------|

| Supply Voltage±7.5VRF Gain Stage Differential Input Voltage±5.6V         | AGC Acqu<br>AGC Hold   |

| Storage Temperature Range<br>AD890JP, AD890JQ 65°C to + 150°C            | Gain Set<br>Input Clar |

| Operating Temperature Range <sup>1</sup><br>AD890JP, AD890JQ 0 to + 70°C | input our              |

| Lead Temperature Range (Soldering 60sec) + 300°C                         |                        |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended

| Logic Assignments | Bit 0 | Bit 1 |

|-------------------|-------|-------|

| AGC Acquire       | 0     | 0     |

| AGC Hold          | 0     | 1     |

| Gain Set          | 1     | 0     |

| Input Clamp       | 1     | 1     |

#### **ORDERING GUIDE**

|               | 1 ackage      | ATTCC                           |

|---------------|---------------|---------------------------------|

| Package       | Options       | (10K)                           |

| 24-Pin Cerdip | Q-24          | \$10.00                         |

| 28-Pin PLCC   | P-28A         | \$ 7.50                         |

|               | 24-Pin Cerdip | PackageOptions24-Pin CerdipQ-24 |

Daalaaa

Driga

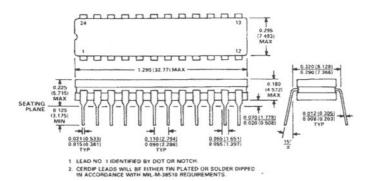

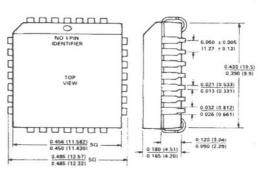

**OUTLINE DIMENSIONS** Dimensions shown in inches and (mm).

#### 24-Pin Cerdip Package

28-Pin PLCC Package

-3-

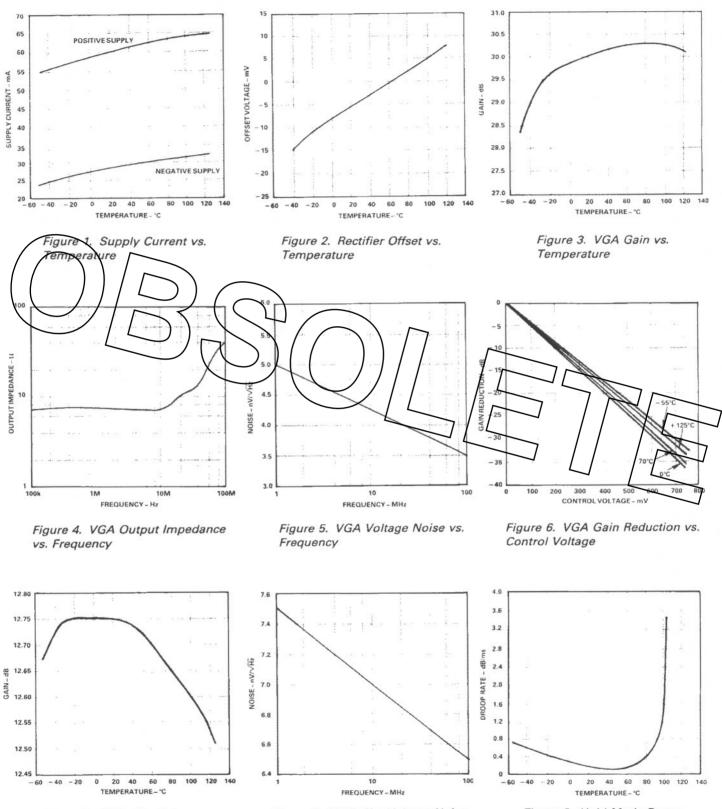

### Typical Characteristics @ + 25°C with ± 5V Supplies

Figure 7. X4 Buffer Gain vs. Temperature

Figure 8. X4 Buffer Voltage Noise vs. Frequency

Figure 9. Hold-Mode Droop Rate vs. Temperature

#### GENERAL LAYOUT REQUIREMENTS

Almost 60dB of total gain is available at 100MHz. Care must be taken to ensure good RF practice in the PC layout to avoid oscillations in the 150MHz-350MHz region. A parallel combination of  $0.1\mu$ F and  $0.01\mu$ F ceramic bypass capacitors should be used as close to the supply pins as possible.

Additionally, a single pole RC filter applied at the input of each stage, with a cut off in the region of 100MHz-150MHz, will help avoid oscillation problems. As a general rule, keep the connections to interstage components as short as possible; it is also recommended that any low pass filtering function which may be required by the system be performed between the VGA stage and the first X4 buffer amplifier. A ground plane should be used to surround any interstage components wherever possible. If these simple rules are followed, stable operation should be assured.

RF GAIN STAGES **IASING THE VGA** Stage Th

30dB variable gain stage biased at a potential of one The tiod drop zbove analog ground. No additional de bias is requi but ac coupling is necessary. The bias voltage is maintained ng operation of the clamp. In during normal operation and duri order for the clamp to operate correctly with an emitter follower driven input,  $50\Omega$ -100 $\Omega$  resistors should be placed in series with the input coupling capacitors. These resistors can be u sed in conjunction with a 5.1pF shunt capacitor to limit the input bandwidth to 150MHz. In the case of an open collector driver input with resistive termination, no additional series resistors are required.

The differential outputs have a nominal dc value of 1.5V less than the positive supply. Internal 1300 $\Omega$  resistors provide bias current to the output emitter followers which operate with 2.7mA nominal current. Output drive can be increased by an additional 2.5mA by paralleling external resistors to either the analog ground or the negative power supply. However, caution should be exercised in order to avoid causing excess dissipation for the package. The recommended output level for the VGA is 300mV p-p differential into 200 $\Omega$  loads.

#### The X4 Buffers

The inputs of these stages have no committed dc biasing, and an input bias current path must be provided. This path can normally be supplied via shunt resistors to analog ground which are generally part of the interstage filter termination networks. The inputs can be biased successfully within  $\pm 1.5$ V of analog ground.

Output drive can be increased in a similar manner to that described for the VGA stage. The nominal dc output level is 2.5V with the internal 500 $\Omega$  load resistors connected to analog ground which provides a nominal standing current of 5mA to the output emitter followers. This current can be increased by up to an additional 5mA by paralleling external resistors to either analog ground or the negative power supply. As before, precautions to limit excessive overall power dissipation apply when steps are taken to increase the output drive capability.

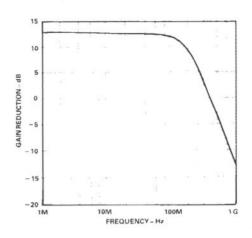

Figure 10. X4 Buffer Frequency Response (100 $\Omega$  in Series with 1 $\mu$ F Load)

#### **OPERATING THE FULL WAVE RECTIFIERS**

The full wave rectifiers consist of two nearly identical stages. Full wave rectification is performed in each stage using two ansistors whose emitters are connected together. The inputs to two full wave rectifiers are biased at one diode drop above the analog ground; therefore, ac coupling is recommended. The full recufier outputs AGC Rectifier" and "Qualifier wave Threshold" - are connected directly to these commoned emitters. Thus, the normal output voltage with zero input signal applied ose to analog ground. The "AGC Redifier" is c pin allows to the output of the rectifier which drives the AGC sample acc and-hold section of the AD890. The "Qualifier Threshold" pin allows access to the output of the threshold rectifier The AGC rectifier has an internal 2kn resistive pull-down

connected between analog ground and the negative power supply pin. The threshold line has no built in pull-down, in order to allow for a peak hold capability during thresholding. If a well controlled rectifier offset is required, an external  $4k\Omega$  pull-down resistor at the "Qualifier Threshold" pin is recommended and will produce a nominal 10mV offset.

#### THE AGC SAMPLE-AND-HOLD

The AGC sample-and-hold section performs averaging of the input waveform to set the RF average output level to 200mV single ended, or 330mV peak for a sinusoidal signal. Thus, without a peak hold capacitor at the "AGC Rectifier" pin, accurate AGC operation only occurs with sinusoidal input signals. An approximate 2mA pull-down current is permanently present at the "AGC Rectifier" pin, and a capacitor may be added here to provide a degree of peak hold for AGC operation within nonsinusoidal fields. A capacitance value of less than 0.03µF or less per µs of transition spacing is recommended. The addition of the capacitor alters the symmetry of the attack and decay rates of the rectifier, which is otherwise symmetric in operation. In order to ensure that the overall AGC response is the same for both high-to-low and low-to-high input level steps, it is necessary to make the rectifier attack and decay times at least a factor of two less than the AGC response time.

The AGC acquire time is approximately 1µs per 1000pF of hold capacitor. A low leakage variety of hold capacitor, such as a silver mica, is necessary to ensure low droop rates. The "Gain Set" pin should be tied to analog ground if not used, in order to prevent excessive leakage which would otherwise affect the hold performance.

The AGC control potential is present at the "Sample-and-Hold Capacitor" pin. If control over open-loop gain is desired, based on AGC control potentials obtained during trial AGC operations, a FET input op amp should be used to buffer this node in order to avoid disturbing the hold operation.

### USING THE AD890 AS A PROGRAMMABLE GAIN AMPLIFIER

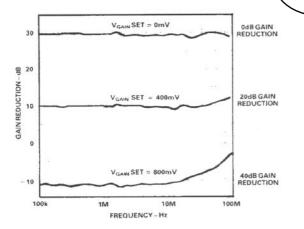

The AD890 is ideally suited for use as an accurate video programmable gain amplifier. If the X4 buffers are utilized with the variable gain amplifier, nearly 60dB of total gain is available at frequencies up to 100MHz. The VGA gain and exponentiator scale factors are trimmed with respect to dc control potentials applied to the "Gain Set" pin. In this mode of operation (see Logic Assignments for bit pattern to be applied to the "Bit 0" and Bi I" pins), a OV ac potential applied to the "Gain Set" produce a nominal VGA gain of 30dB. With an additional pir will ch X4 buffer, total nominal gain is SdB. Each 12 B from ea tage applied will produce a 20r ldB reduction increment of V vol in gain. A simple equation can used to calculate the nominal VGA in this mode gain of VGA Gain (dB) 50)

where VGAIN SET is in volts.

Figure 11. Frequency Response of VGA Gain for Different Gain Set Voltages

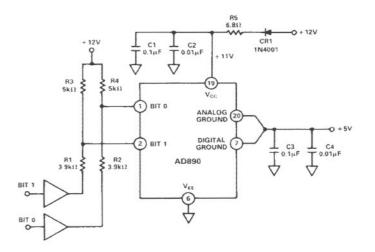

#### **OPERATION WITH +5V, +12V SUPPLIES**

Operation with  $+5V (\pm 0.25V)$  and  $+12V (\pm 1.2V)$  supplies is readily achieved. Figure 12 shows the AD890 configured for +5V, +12V operation. The analog and digital grounds must be connected to the +5V line or to an available center tap of the

Figure 12. AD890 Connection for +5V, +12V Operation

+ 12V supply. Thus connected, a current of approximately 30mA will flow in this line under normal operation. The input clamping action occurs with respect to this line, increasing its current by an additional 12mA or so.

Both the +5V and +12V supplies should be RF bypassed to ground with at least two capacitors: values of  $0.1\mu$ F and  $0.01\mu$ F are recommended. In addition, some higher level of decoupling capacitance such as  $3.3\mu$ F value may be desirable. Next, insert a series-connected  $6.8\Omega$  [74W resistor and 100mA diode in series with the +12V supply. This helps to reduce overdissipation in the chip.

Fower supply decoupling should occur on the circuit side of the resistor-diode network. A second diode can be substituted for the  $6.8\Omega$  resistor if the voltage difference between the two supplies is greater than 5.6 volts.

Finally, mode control is achieved by using open collector drivers and resistors as shown; 5.1V Zener diodes can be substituted for resistors R1 and R2. Internal diode clamping in the AD890 permits this mode of operation.

The mode switching times will be affected by resistor values chosen; this is due to the RC time constants formed by the resistors in conjunction with the input capacitance of the chip package.

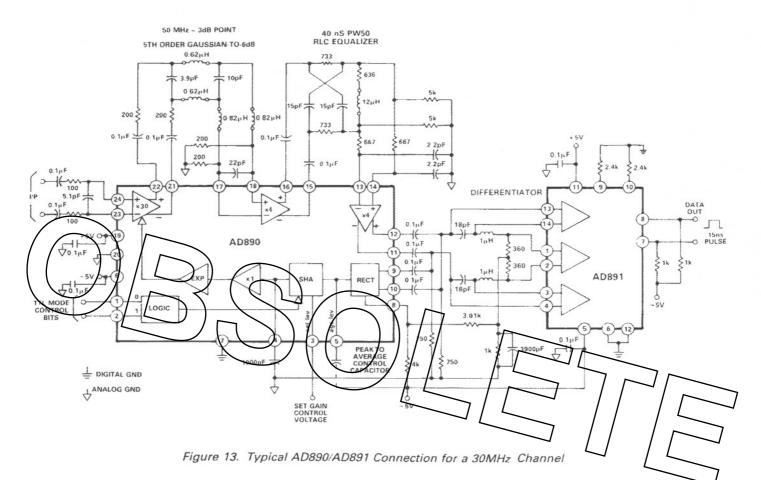

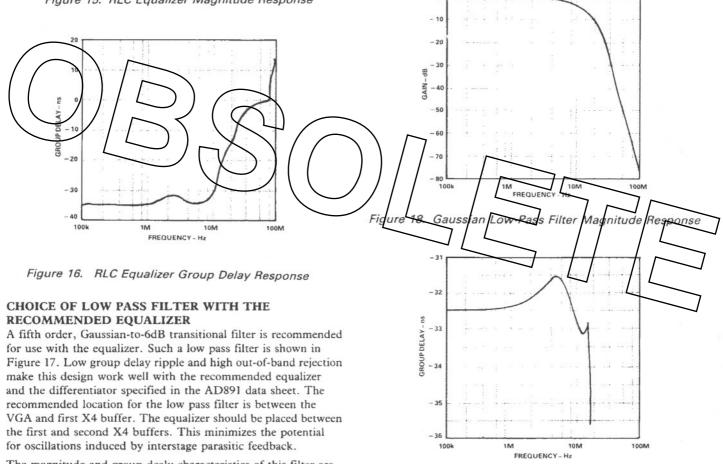

## INTEGRATING WITH THE AD891 RIGID DISK DRIVE DATA QUALIFIER

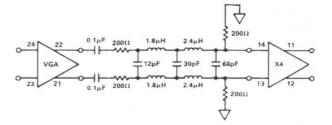

Figure 13 shows a typical application using the AD890 and AD891 connected together to create a 30MHz channel (cerdip connections shown). This circuit includes a 5-pole 30MHz Gaussian-to-6dB transitional filter plus a second-order RLC time domain equalizer. A typical second-order, fully differential, passive delay-line differentiator interface for the AD891 is also included. (For a more detailed description of the delay-line differentiator, see the AD891 data sheet.) The analog and digital grounds should be connected at the power supply common.

#### **USING EQUALIZERS WITH THE AD890**

The AD890 is ideal for applications where equalization is employed. The X4 buffer output drivers are designed to operate into 200 $\Omega$  loads, making tapped delay-line designs easy. Sum and differencing of different tap weights can be achieved by simple resistive dividers.

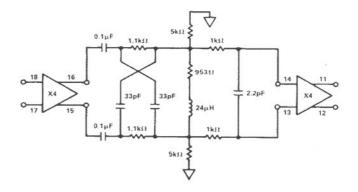

As an alternative, a simple RLC network can be implemented to provide a low-cost, fully differential alternative to the three-tap, tapped delay-line equalizer which often is used for pulse slimming. Essentially, the equalizer shown in Figure 14 consists of an RC lattice, which provides the magnitude characteristic, together with an LR shunt section which acts to define the overall passband group delay and the ratio of minimum to maximum gains within the passband.

The network shown approximates a function of the form:

$F(\omega \tau) = 1 - k \cos \omega \tau$ , where k = 0.6, and  $\tau = 36$  ns.

The circuit is optimized for a 120ns transition PW5O. Altering the 953 $\Omega$  resistor and the 24 $\mu$ H inductor can change both k and  $\tau$ , permitting cylinder dependent equalization to be performed, thus minimizing problems of overequalization. To alter k, the ratio of the 1.1k $\Omega$  and 953 $\Omega$  resistors should be changed. To alter  $\tau$ , the reactive element should be scaled proportionally. The equalizer in Figure 13 is optimized for k = 0.6 and  $\tau$  = 12ns.

Figure 14. RLC Equalizer

It is important to note the benefits of fully differential (as opposed to single-ended) operation: 1) reduced harmonic distortion due to symmetric operation; 2) improved power supply noise rejection; 3) less insertion loss, allowing for reduced gain and, hence, improved distortion in stages prior to the equalizer.

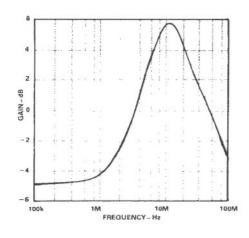

The magnitude and group delay characteristics of this equalizer are shown in Figures 15 and 16, respectively.

Figure 15. RLC Equalizer Magnitude Response

Figure 17. 5th Order Gaussian-to-6dB Transitional Filter

The magnitude and group dealy characteristics of this filter are shown in Figures 18 and 19, respectively.

The magnitude and group dealy characteristics of this filter are shown in Figures 18 and 19, respectively.

Figure 19. Gaussian Low-Pass Filter Group Delay Response

C1177 - 10 - 4/88